상호: 주식회사 와이지넷코리아 (YOUNG GROUP NET KOREA CO., LTD.) 대표: 주용규 사업자등록번호: 223-81-14426 통신판매업신고번호: 제 2015-서울강남-02499호

우편번호 : 07505 서울시 강서구 하늘길210 김포국제공항 구화물청사 4번GATE 361-4호

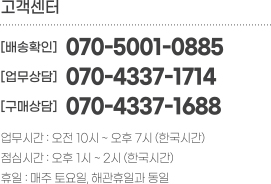

TEL:(배송확인) 070-5001-0885 (업무상담) 070-4337-1714 업무제휴문의:ygnkorea@gmail.com

웨이하이센터상호: 威海韩运国际贸易有限公司 法定代表人: 朱 勇奎 统一社会信用代码: 91371000MA3U6XGW6N 进出口: 37109409C6

(264200) 山东省 / 威海市 / 环翠区 / 西苑街道 / 贝卡尔特路91-2号 / 威广物流园西门 / 韩运国际贸易 TAPL

TEL : +86) 0631- 598 -1400 FAX : +86) 0631- 598 -1144

TAPL Hanyun International Trade , West Gate of Weihai Logistics Park, Bekart Road-91, Xiyuan Street, Huancui District, Weihai City, Shandong Province,CHINA (ZIPCODE 264200)

Copyright© 2023-2024 alitapl.com All Rights Reserved